高温成膜したチタン酸バリウムストロンチウム薄膜を用いた可変容量の集積化プロセス

森脇 政仁<sup>†</sup> 据露伊保龍<sup>††</sup> 門田 道雄<sup>††</sup> 江刺 正喜<sup>†††</sup> 田中 秀治<sup>†a)</sup>

Integration Process of Variable Capacitors Using Barium Strontium Titanate Thin Film Deposited at High Temperature

Nobuyoshi MORIWAKI†, Ivoyl P. KOUTSAROFF††, Michio KADOTA††, Masayoshi ESASHI†††, and Shuji TANAKA†a)

あらまし チタン酸バリウムストロンチウム (BST) を用いた可変容量を集積回路上に形成するために、別の Si 基板に成膜した BST をポリイミドを介して集積回路基板に接合し、Si 基板をエッチングで除去することに よって BST 膜を集積回路基板にトランスファする集積化プロセスを開発した。誘電率可変特性に優れる BST は 高温で成膜しなくてはならないが、このトランスファ法によって耐熱性の低い基板上でも BST 膜を利用できる. プロセスの途中で BST 膜が SF $_6$ /Ar プラズマにさらされると、BST 膜表面に誘電率の低い Ba と Sr のフッ化 物が形成され、BST 膜の見かけ上の誘電率が低下することが分かった。この問題について実験的検証と考察を行い、BST 膜の劣化を防ぐプロセスを構築し、ダミー回路基板上に BST 可変容量を作製した.

キーワード チタン酸バリウムストロンチウム (BST), 可変容量, トランスファ法, プラズマダメージ

# 1. まえがき

無線通信応用では、周波数可変やインピーダンス整合のために可変容量が必要である。現在、可変容量としてpn接合に逆バイアス電圧をかけて容量を変化させるバラクタダイオードが利用されているが、Q値が低いため用途が限られる。例えば、可変 SAW (surface acoustic wave) フィルタを可変容量を用いて構成する場合、そのQ値が挿入損やカットオフ特性に影響する。一方、Q値に優れた可変容量としては、エアギャップを機械的に変化させる MEMS (micro electro

mechanical systems) 可変容量があり、可変 SAW フィルタへの適用例も報告されている [1]. しかし、エアギャップは典型的には  $1\sim3\,\mu\mathrm{m}$  程度で、当然、誘電率は 1 であるので、容量を大きくすると面積が過大になる。これはデバイス小形化の観点から問題であるだけではなく、応力によって構造体が変形しやすくなることからも問題である。また、MEMS 可変容量のアクチュエータとして静電方式を用いた場合、プルインのため電圧制御できるのはエアギャップの 3 分の 1 まで、アナログ的な容量変化幅はたかだか 150%である。

強誘電体材料であるチタン酸バリウムストロンチウム (BST) は,電界印加によって誘電率が大きく変化する材料 [2]  $\sim$  [5] で,1300%にも達する可変幅も報告されている [6]. また,他の強誘電体材料と比較して,BST は高周波領域でも誘電正接  $(\tan\delta)$  が小さく,つまり可変容量を構成した場合,Q値が比較的高く,しかも非鉛材料であるために環境に優しい.したがって,BST を用いた可変容量は,フィルタやアンプと組み合わせて,周波数可変やインピーダンス整合といった機能を実現するのに適している.また,BST の誘電

<sup>†</sup> 東北大学大学院工学研究科,仙台市

Graduate School of Engineering, Tohoku University, 6-6-01 Aza Aoba, Aramaki, Aoba-ku, Sendai-shi, 980-8579 Japan

<sup>†† (</sup>株) 村田製作所技術·事業開発本部, 野洲市 New Technology & Products Development Group, Murata Manufacturing Co., Ltd., 2288 Oshinohara, Yasu-shi, 520-2393 Japan

<sup>†††</sup> 東北大学原子分子材料高等研究機構, 仙台市 WPI-AIMR, Tohoku University, 6-6-01 Aza Aoba, Aramaki, Aoba-ku, Sendai-shi, 980-8579 Japan

a) E-mail: tanaka@mems.mech.tohoku.ac.jp

率は数百程度であり、可変容量の小形化という点でも MEMS 可変容量と比較して有利である。

しかし、誘電率可変能に優れる BST は、成膜に 600°C 程度の高温を要するため、そのような高温加熱が許される基板、典型的にはベアのサファイア基板や Si 基板にしか成膜できない、様々な応用を考えると、BST を集積回路、樹脂(フレキシブル回路)、圧電材料などの上で利用したいが、そのためには、いったん、別の基板に成膜した BST を所望の基板やデバイスに移す(トランスファする)方法が考えられる。これまでに、Si 基板に成膜した BST をポリイミドシート [7]、LiNbO3 基板 [8]、及び液晶ポリマシート [9] にトランスファし、可変容量を作製した研究が報告されている。

本研究では、標準的な集積回路基板に BST 可変容量をトランスファ法によって形成する技術を開発した. そのために、別の Si 基板に成膜した BST を樹脂を介して集積回路基板に接合し、Si 基板を除去した上で集積回路と電気的に接合する工程が必要であるが、このような集積化プロセスはこれまでに報告されていない.

# 2. プロセス開発とデバイス試作

#### 2.1 試作デバイスの構造

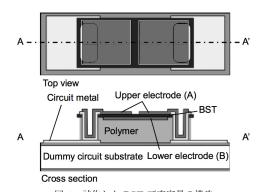

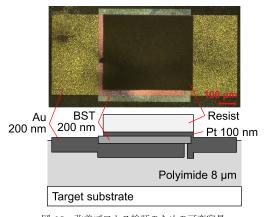

図1に試作デバイスの構造を示す。可変容量は MIM (metal-insulator-metal) 構造を有し、BST 薄膜の下部電極(図中 B)を通じて二つの MIM 構造が直列に接続されている。可変容量と基板とは樹脂によって接合され、可変容量の上部電極(同 A)と基板上の薄膜配線とが、樹脂に形成された開口部を介して Au めっきで接続されている。本研究の目的は、BST 可変容量の集積化プロセスを開発することにあるので、集積回

図 1 試作した BST 可変容量の構造 Fig. 1 Structure of prototyped BST variable capacitor.

路基板の代わりに、酸化膜付き Si 基板に Cr/Pt/Au の薄膜配線を形成したもの(ダミー回路基板)を用いた。ただし、同様のプロセスを集積回路基板上で行っても集積回路が損傷しないように、集積化プロセスの最高温度は  $350^{\circ}C$  とした。

#### 2.2 集積化プロセス

## 2.2.1 集積化プロセスの概要

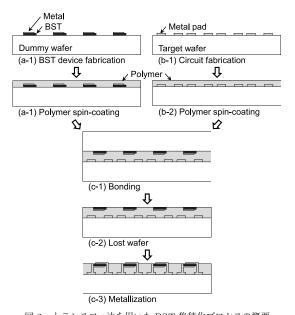

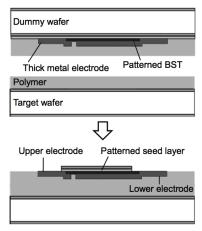

図 2 に集積化プロセスの大まかな流れを示す. Si 基板に BST を高温成膜し、後に下部電極となる電極を形成した後、接合用樹脂を塗布する(2.2.2 で詳述). 別途、ダミー回路基板を用意し、同様に接合用樹脂を塗布する(2.2.3 で詳述). 両基板を重ね、力と熱を加えながら接合する. BST 側の Si 基板をエッチングで除去し、BST 薄膜をダミー回路基板にトランスファする. BST 薄膜の表面に上部電極を形成し、接合用樹脂に穴を開けて上部電極とダミー回路基板とを接続する(2.2.4 で詳述). なお、この段階で接合用樹脂を $O_2$  プラズマアッシングによって除去すれば、BST のMIM 構造が自己支持された構造が得られるが、これは赤外線センサに利用可能である.

## **2.2.2** BST の成膜とパターニング

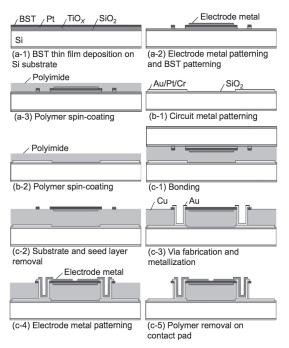

図 3 に具体的な工程を示す。同図の a-1 $\sim$ 3 が BST 成膜用 Si 基板の工程である。 $500 \mu m$  厚の (100) Si 基板に拡散防止層となる 50 nm 厚の SiO<sub>2</sub> を熱酸化に

図 2 トランスファ法を用いた BST 集積化プロセスの概要 Fig. 2 Concept of BST integration process using transfer method.

図 3 実証した BST 集積化プロセス Fig. 3 Demonstrated BST integration process.

よって形成し、その上に  $10 \, \mathrm{nm}/100 \, \mathrm{nm}$  厚の  $\mathrm{TiO}_x/\mathrm{Pt}$  を成膜する。 $\mathrm{TiO}_x$  は  $\mathrm{SiO}_2$  と  $\mathrm{Pt}$  との密着層であり、高周波マグネトロンスパッタ法によって  $200^{\circ}\mathrm{C}$  で成膜する。 $\mathrm{Pt}$  は  $\mathrm{BST}$  を配向させるためのシード層であり、同様に  $550^{\circ}\mathrm{C}$  で成膜する。 $\mathrm{Pt}$  は (111) に配向し、その上の  $\mathrm{BST}$  も (111) に優先配向する。 $\mathrm{BST}$  も 高周波マグネトロンスパッタ法によって成膜する (a-1)。成膜温度は  $650^{\circ}\mathrm{C}$ 、膜厚は  $120 \, \mathrm{nm}$  である。 $\mathrm{BST}$  ターゲットにおけるチタン酸バリウム ( $\mathrm{BTO}$ ) とチタン酸ストロンチウム ( $\mathrm{STO}$ ) との比は 7:3 であるが、これは可変容量に適した比といわれている。

BST 表面に後の下部電極を形成するが、イメージリバーサルフォトレジスト(AZ5214E、AZ エレクトロニックマテリアルズ)を用いたリフトオフ法を利用する。下部/上部電極の材料は、可変容量としてはPt がよく用いられるが、本実験では赤外線センサへの応用も想定し、NiCr としている。BST 膜のパターニングは、ポジフォトレジスト(OFPR-800、東京応化工業)をマスクに用いて、反応性イオンエッチング(reactive ion etching、RIE)によって行う(a-2)。RIE 装置は平行平板型(L-201D-L、キヤノンアネルバ)であり、基板ステージは  $7~10^{\circ}$ C に水冷されている。RF パワーは  $100~W/\phi3''$ 、エッチングガスは

$Ar/CHF_3$  (34 sccm/6 sccm), プロセス圧は 5 Pa である. この条件で, BST のエッチレートは 3 nm/min, BST/フォトレジストの選択比は 0.1 である.

接合用樹脂として感光性ポリイミド (UR-3100E, 東レ)をスピン塗布する.このときポリイミド液の粘度が高いため,基板端部に液が溜まり,その部分のポリイミドが厚くなる.このエッジビードは後の基板接合に不都合なので,基板端部を除いて感光し,現像によって基板端部のポリイミドを除去する.その後, $N_2$ 雰囲気,350°Cでポリイミドをフルキュアし,その上に,もう1層ポリイミドを同条件で塗布し,フルキュアする.ただし,2層目のポリイミドはパターニングしない.その結果,エッジビードのない接合樹脂層が得られ、中央部分の厚さは3 $\mu$ mになる(a-3).

#### 2.2.3 ダミー回路基板の作製

図 3 の b-1, 2 がダミー回路基板の工程である.  $500\,\mu\mathrm{m}$  厚の (100) Si 基板を酸化し、 $50\,\mathrm{nm}$  厚の  $\mathrm{SiO}_2$  を形成する。その上に、 $10\,\mathrm{nm}/10\,\mathrm{nm}/100\,\mathrm{nm}$  厚の  $\mathrm{Cr/Pt/Au}$  からなる薄膜配線を、イメージリバーサルフォトレジストを用いてリフトオフ法によって形成する (b-1). Cr は密着層、 $\mathrm{Pt}$  は拡散防止層である.

ダミー回路の裏側に後の接合 (c-1) で基板同士を位置決めするためのアラインメントマークを形成する. アラインメントマークは光学顕微鏡で視認できれば何でもよいが、ここでは、Si 基板を RIE によってわずかに窪ませて形成する(基板の端部に形成するため図3では省略されている). その後、既に述べた方法でダミー回路基板の表面に接合用ポリイミドを塗布する.

2.2.4 BST 薄膜のトランスファと可変容量の作製BST を成膜した Si 基板とダミー回路基板とを,マスクアライナ (MA6, Süss MicroTec)を用いて位置決めし,ウェーハ接合装置 (SB6e, Süss MicroTec)を用いて真空中で900kPaの接合圧を加えて350°Cに加熱し,1時間保持して接合する(c-1).接合条件は文献[10]に基づいて決めたが,均一に接合するためには,接合前にポリイミドをフルキュアしておくことが鍵である.ポリイミドをフルキュアせずに接合すると,イミド化の際に発生する水分によってボイドが発生する.

基板接合後、BST を成膜した Si 基板を除去し、BST 膜をダミー回路基板にトランスファする。Si 基板のほとんどを SF6 を用いた RIE によって除去し、残った Si を  $XeF_2$  ガスエッチングによって除去する。これは、RIE 時、エッチレートの不均一性によって Si が完全に除去された部分とそうでない部分とが生じるが、その

まま RIE を続けるとイオン衝撃で下層にダメージが入るためである。なお,RIE は研削・研磨に換えることもできる。この状態で,ダミー回路基板表面にはシード層である  $Pt/TiO_x$  が露出している。本来, $TiO_x$  は  $XeF_2$  によってエッチングされるはずであるが,この  $TiO_x$  は高温プロセス中の拡散によって純粋な  $TiO_x$  になっていないので,Pt 上に残る。シード層を既出の 平行平板型 RIE 装置で  $SF_6/Ar$  ( $30 \operatorname{sccm}/3 \operatorname{sccm}$ ) を 用いてエッチングし,完全に除去する (c-2). 4. で述べるが,この工程は改善する必要がある。

次に、ポリイミド層に RIE によって可変容量とダミー回路基板とを接続するための開口部を形成する. そのマスクとして、200 nm 厚の Al を成膜し、フォトエッチングによってマスクパターンを形成する. 既出の平行平板型 RIE 装置で  $O_2/CF_4$  ( $32 \operatorname{sccm}/8 \operatorname{sccm}$ )を用いてエッチングする. なお、Al マスク形成前の状態のように、基板上に屈折率の異なる誘電体多層膜が存在すると、そこからの多重反射によってフォトリソグラフィが困難になり、そのような場合、BARC (bottom anti-reflection coating) が必要になる. この点から、リフトオフ法ではなく、Al を全面成膜し、フォトエッチングによってマスクを形成する方がよい. ポリイミド層の RIE 後、Al マスクを剥離する.

形成したポリイミドの開口部を Au めっきで埋め、 電気的接続部とする. めっきに先立ち, シード層と なる 100 nm 厚の Cu を全面成膜し、ポジフォトレ ジスト (OFPR-800, 東京応化工業) を用いてめっ きしない部分を覆う. 市販のノンシアン Au めっき 液 (MICROFAB Au310, 日本エレクトロプレーテ ィング・エンジニヤース)を用いて,50°Cの浴温,  $0.4\,\mathrm{A/dm^2}$  の電流密度で 20 分間めっきし、約  $3\,\mu\mathrm{m}$ の膜厚を得る. 不要なシード層をエッチングした後, 可変容量の上部電極 (30 nm 厚 NiCr) をリフトオフ 法によって形成する (c-4). 最後に, 不要なポリイミ ドを $O_2$ プラズマアッシングによって除去する (c-5). この際, 長時間アッシングすることで可変容量の下の ポリイミドも除去し、自己支持構造を得ることもでき る. ただし、MIM 構造に狭い間隔で穴を開け、そこ を通してアッシングが進むようにしなければ、非現実 的に長い時間が必要である.

# 3. 試作結果と考察

## 3.1 試作結果

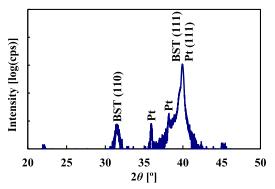

成膜した BST の X 線回折スペクトルを図 4 に示

図 4 Si 基板に成膜した BST の X 線回折スペクトル Fig. 4 X-ray diffraction spectrum of BST deposited on Si substrate.

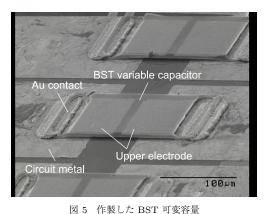

図 5 作聚した BST 可変谷軍 Fig. 5 Completed BST variable capacitor.

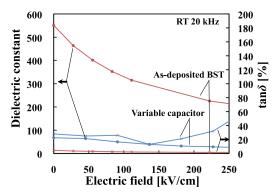

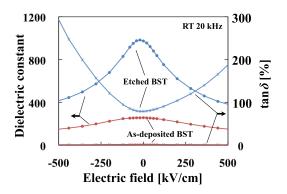

す. 高温スパッタ成膜によって (111) に優先配向していることが分かる. 図 5 に作製した BST 可変容量を示す. その容量可変特性を, LCR メータ (HP 4284A)を用いて, 周波数 20 kHz, 常温で評価した. 測定結果を図 6 に示す. 横軸は印加直流電圧を BST 膜厚で割った印加電界である. 2.2.2 に述べた方法で成膜した BST にリフトオフ法で Pt 電極を形成しただけのものは, 膜厚方向に電界を印加すると誘電率が低下し, 150 kV/cm² の印加で誘電率は約半分になる. BST 膜厚が 120 nm なので, 印加電圧は 1.8 V であり, 標準的な集積回路によって制御できる.

一方,作製した可変容量は,電界印加によって容量が減少する傾向を示すものの,成膜直後のBSTと比べると,その誘電率が大幅に低下した.可変容量の電圧非印加時の容量をBSTの比誘電率に換算すると約70となり,成膜直後の約550と比べて1/8程度になっている.以上のことから,上述の集積化プロセス

図 6 作製した可変容量と電極を形成しただけの BST 膜 の比誘電率と誘電正接の印加電界依存性

Fig. 6 Electric field dependency of dielectric constant and  $\tan\delta$  of variable capacitor and asdeposited BST film.

によって可変容量の形状を作製できることは実証できたものの、BST の劣化を引き起こす工程があることが分かった。

## 3.2 BST 劣化に関する考察

RIE にさらされた BST 表面は損傷を受け、その誘電率や耐電圧が低下し、漏れ電流が増えることが知られている [11], [12]. 具体的な損傷は、プラズマからの紫外線とイオン衝撃による結晶構造の破壊、あるいはハロゲン化物への変質である。 文献 [12] では、成膜直後に厚さ  $300\,\mathrm{nm}$  の BST 膜の比誘電率が 240 であったのに対して、 $\mathrm{CF_4/Ar}$  (20%/80%) を用いて  $1\,\mathrm{分間}$ , RIE 後、130 に低下したと報告されている。ここで、RIE による変質層の厚さを仮定すると、その比誘電率を次の式から見積もられる。

$$\varepsilon_{\text{etched}} = \frac{\varepsilon_{\text{D}}\varepsilon_{\text{N}}}{\varepsilon_{\text{D}}h_{\text{N}} + \varepsilon_{\text{N}}h_{\text{D}}}(h_{\text{N}} + h_{\text{D}}) \tag{1}$$

ここに  $\varepsilon_{\text{etched}}$  は RIE 後の見かけの比誘電率,  $\varepsilon_{\text{N}}$ ,  $\varepsilon_{\text{D}}$  はそれぞれ正常層, 変質層の比誘電率,  $h_{\text{N}}$ ,  $h_{\text{D}}$  はそれぞれ正常層, 変質層の膜厚である. ここで,  $h_{\text{D}}=10\,\mathrm{nm}$  を仮定して上の例で  $\varepsilon_{\text{D}}$  を見積もると,  $\varepsilon_{\text{D}}=9$  となる.

本研究でも,図 3 (c-2) の工程でシード層の  $Pt/TiO_x$  を  $SF_6/Ar$  を用いて RIE した際,同様の損傷が BST に生じた可能性がある.ここで, $h_D=10$  nm, $\varepsilon_D=9$  を仮定すると,式 (1) から  $\varepsilon_{\rm etched}=92$  が得られ,これは測定された比誘電率 70 と同程度である.このことから,薄い BST 膜では,極薄い表面層が RIE 等によって変質しても,見かけの誘電率が大きく低下することが分かる.

## 4. プロセス改善のための検討

## 4.1 BST 変質の検証実験

上述の検討から、比誘電率低下の原因として、 $SF_6/Ar$  を用いた RIE によって BST 表面に低誘電率層が形成されたことが疑われる。そこで、この仮定を検証するための実験を行った。

## 4.1.1 実験方法

可変容量を作製したときと同様に(2.2.2 を参照),Si 基板に  $TiO_x/Pt$  のシード層を形成し, $200 \, nm$  厚の BST を成膜する.初期状態として,その表面を XPS (X-ray photoelectron spectroscopy) によって分析する.その後, $100 \, nm$  厚の Pt 電極をリフトオフ法によって形成し,比誘電率の印加電界依存性を評価する.

次に、上述の Pt 電極を、図 3 (c-2) の工程と同様に  $SF_6/Ar$  を用いた RIE によって除去し、その表面を XPS によって分析する.また、比較試料として、 Pt 電極を Ar のみを用いてスパッタエッチングした試料 も用意する.それらの上に、再びリフトオフ法によって Pt 電極を形成し、比誘電率の印加電界依存性を評価する.

### 4.1.2 実験結果

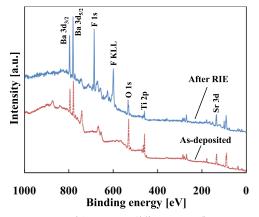

図 7 に XPS の結果を示す。 $SF_6/Ar$  を用いた RIE の後,成膜直後の BST には見られなかった F のピークが現れた。また,BST を構成する金属元素について RIE の影響を見ると,表面において Ba は増え,Sr は増減せず,Ti は減っていることが分かる。BST の RIE では,Ti は F ラジカルと反応して,蒸気圧の高いフッ化物となって揮発する。一方,蒸気圧の低い Ba と Sr のフッ化物はそのままでは揮発せず,Ar イオンによってスパッタエッチングされるものの,表面に残りやすいと考えられる。上述の XPS 結果はこの RIE の原理を支持するものであり,RIE 後の表面に Ba と Sr のフッ化物が存在することを示唆している。

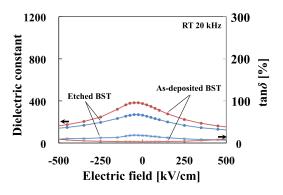

図 8 に、 $SF_6/Ar$  を用いた RIE 後 (a),及び Ar スパッタエッチング後 (b) の比誘電率の印加電界依存性 を,BST の成膜直後,つまりエッチング前のそれと比較して示す.図 8 (a) から分かるように,RIE によって比誘電率が減少しており,これは 3.1 に述べた試作結果と一致する.一方,図 8 (b) に示すように,Ar スパッタエッチングによっては比誘電率が増加した.

### 4.1.3 考 察

以上に述べた結果と 3.2 に述べた考察を合わせ、以下のように結論できる、 $SF_6/Ar$  を用いた RIE にさら

図 7  $SF_6/Ar$  を用いた RIE 前後での BST 膜の XPS の 結果

Fig. 7  $\,$  XPS result of BST film before and after RIE with SF  $_{6}/{\rm Ar}.$

した BST 表面には、誘電率の小さな Ba と Sr のフッ 化物が形成される. その結果、BST 膜の見かけの誘電率は、成膜直後のそれより大幅に低下する. このような見かけの誘電率の低下は、BST 膜表面が有機物で汚染されていても起こる. 図 8 に示したエッチング前のBST の比誘電率は、無電界時に 400 程度と一般的な値 (800~1000) と比べて小さいが、これは試料準備時(例えば、リフトオフ時)に試料が汚染された可能性を示唆している. 一つの可能性として、Ar スパッタエッチングによって汚染層が除去され、また、電極を再形成した際は汚染が起こらず、その結果、図 8 (b) に示したように比誘電率が 1000 程度に増加したと考えると、実験結果を説明できる. ただし、Ar スパッタエッチングは BST 表面に物理的ダメージを与え、 $\tan\delta$ も同時に増加させることに注意しなくてはならない.

以上のことから、BST 膜の見かけの誘電率低下を防ぐためには、BST 表面を清浄に保ち、かつフッ素系ガスのプラズマにさらさないことが必要である。また、イオン衝撃にさらすことも、損失増大を防ぐために避けなくてはならない。

## 4.2 改善プロセスの提案と検証

## 4.2.1 改善プロセス

以上に述べたことから,BST が  $SF_6/Ar$  プラズマにさらされる図 3(c-2) の工程を改善する必要がある.ここでの問題は,シード層である  $TiO_x/Pt$  を RIE によって全面的に除去することであり,図 9 に示すように工程を改善すればよいと考えられる.改善の要点は,シード層を全面的に除去するのではなく,パターニン

(a) SF<sub>6</sub>/Ar を用いた RIE 前後での測定結果 (a) Measurement results before and after RIE with SF<sub>6</sub>/Ar.

(b) Ar スパッタエッチング前後での測定結果

- (b) Measurement results before and after Ar sputter-etching.

- 図 8 エッチング前後での BST 膜の比誘電率と誘電正接 の印加電界依存性

Fig. 8 Electric field dependency of dielectric constant and  $\tan\delta$  of BST film before and after etching.

グして可変容量の上部電極として利用することである. 以下に変更点を具体的に述べる.

まず、図 3 (a-2) の工程で、BST のパターニングを  $Ar/CHF_3$  を用いた RIE からウェットエッチングに変更する。エッチャントには HF、NH4F、HNO3、 $H_2O$  を 3:14:8:75 の重量比で混合したものを用い [13]、マスクには  $1\mu$ m 厚のポジフォトレジスト (OFPR-800、東京応化工業)を用いる。この変更によって、シード層である  $TiO_x/Pt$  はエッチングされずに残るが、a-3 の工程で作製する電極の形状変更と合わせ、可変容量の電気的接続を容易にする。後の下部電極をリフトオフ法によって 200 nm 厚の Au で形成した後、接合用樹脂を塗布した状態が図 9 の上に示すものである。

図 9 BST へのダメージを防ぐために改善したトランス ファプロセス

Fig. 9 Transfer process improved to avoid damage to BST.

次に、c-1 の工程と同様に BST を成膜した Si 基板 とダミー回路基板とを接合する. 続いて BST を成膜した Si 基板を除去するところまでは同じであるが、既に述べたようにシード層である  $TiO_x/Pt$  層は全面除去せず、これをパターニングして上部電極とする. シード層のパターニングは、 $4\mu m$  厚のポジフォトレジスト(OFPR-800、東京応化工業)をマスクにして、 $Ar/CHF_3$  を用いた RIE によって行う. これによって図 9 の下に示す構造が得られる. 以降、ダミー回路基板との電気的接続は従前の工程で可能である.

## 4.2.2 実験結果

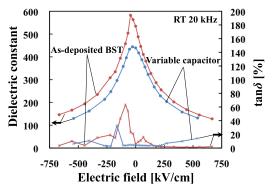

図 10 に改善プロセスの検証のために作製したデバ イスを示す. また、図 11 に、検証デバイス作製前後で の比誘電率の印加電界依存性を示す. 検証デバイス作 製前、つまり電極を形成しただけの BST 膜と比較し て、検証デバイスで測定された比誘電率は10~20%の 低下に留まった. 電界印加による比誘電率の変化率に も  $\tan \delta$  にも顕著な変化は見られない。 $-100\,\mathrm{kV/cm}$ 付近に見られる tan δ の急激な変化の原因は不明であ るが、可変容量両側の電極材料が Pt, Au と異なるこ とが、印加電界方向による特性の違いに影響している 可能性がある[14]. 以上の結果から、提案した改善プ ロセスが有効であることを実証できた. なお、BST の 誘電率は膜応力にも影響されることが知られており、 BST を成膜した Si 基板を除去したことによって、1~ 2GPa の引張応力が解放され、誘電率が検証デバイス 作製前後で変化した可能性もある.

図 10 改善プロセス検証のための可変容量 Fig. 10 Variable capacitor for testing improved process.

図 11 検証用可変容量と電極を形成しただけの BST 膜 の比誘電率と誘電正接の印加電界依存性

Fig. 11 Electric field dependency of dielectric constant and  $\tan \delta$  of test variable capacitor and as-deposited BST film.

## 5. t t び

BST を用いた可変容量を集積回路上に形成するために、別の Si 基板に高温成膜した BST をポリイミドを介して集積回路基板に接合し、Si 基板を除去することによって、BST 膜を集積回路基板にトランスファするプロセスを開発した。本研究では、実際の集積回路基板の代わりにダミー回路基板を用いたが、開発したプロセスは集積回路基板上でも実施しうるものである。

最初に作製した可変容量は、作製途中で BST 膜が  $SF_6/Ar$  プラズマにさらされたことによって、BST 膜表面に誘電率の低い Ba と Sr のフッ化物が形成された と考えられる。その結果、BST 膜の見かけ上の誘電率 が大きく低下した。この問題について実験的検証と考

察を行い、それに基づいて一部の工程を改善した.改善プロセスでは、BST膜の誘電率の顕著な低下は見られず、研究目的を達することができた.

開発した集積化プロセスは、BST 以外の機能性材料にも適用可能であり、様々なデバイスの機能集積化や小形化に資すると期待される.

謝辞 本研究は、最先端研究開発支援プログラム「マイクロシステム融合研究開発」(中心研究者:江刺正喜)の一環として実施した。本研究に対して多大な支援を頂いた村田製作所の木村哲也氏に感謝致します。

#### 文 献

- T. Yasue, T. Komatsu, N. Nakamura, K. Hashimoto, H. Hirano, M. Esashi, and S. Tanaka, "Wideband tunable Love wave filter using electrostatically actuated MEMS," Sens. Actuators A, vol.188, pp.456– 462, 2012.

- [2] X. Zhu, J. Zhu, S. Zhou, Z. Liu, N. Ming, S. Lu, H.L.-W. Chan, and C.-L. Choy, "Recent progress of (Ba,Sr)TiO<sub>3</sub> thin films for tunable microwave devices," J. Electr. Mater., vol.32, no.10, pp.1125–1134, 2003.

- [3] S. Gevorgian and A. Vorobiev, "Substrates, varactors and passive components," in Ferroelectrics in Microwave Devices, Circuits and Systems Engineering Materials and Processes, pp.115–173, Springer-Verlag, Berlin, 2009.

- [4] I.P. Koutsaroff, T.A. Bernacki, M. Zelner, A. Cervin-Lawry, T. Jimbo, and K.K. Suu, "Characterization of thin-film decoupling and high-frequency (Ba,Sr)TiO<sub>3</sub> capacitors on Al<sub>2</sub>O<sub>3</sub> ceramic substrates," Jpn. J. Appl. Phys., vol.43, no.9B, pp.6740–6745, 2004.

- [5] J.S. Cross and I.P. Koutsaroff, "Review on ferroelectric thin film devices: Fundamental aspects and integration challenges," 耐火物, vol.62, no.4, pp.162-174, 2010.

- [6] N.K. Pervez, P.J. Hansen, and R.A. York, "High tunability barium strontium titanate thin films for rf circuit applications," Appl. Phys. Lett., vol.85, no.19, pp.4451–4453, 2004.

- [7] K.-I. Park, S.Y. Lee, S. Kim, J. Chang, S.-J.L. Kang, and K.J. Lee, "Bendable and transparent barium titanate capacitors on plastic substrates for high performance flexible ferroelectric devices," Electrochem. Solid-State Lett., vol.13, no.7, pp.G57-G59, 2010.

- [8] H. Hirano, T. Kikuta, M. Esashi, and S. Tanaka, "Thin film transfer technology for tunable SAW filter using integrated ferroelectric varactors," 2011 IEEE International Ultrasonics Symposium, pp.1960–1963, Orlando, Florida, USA, Oct. 2011.

- [9] Y. Shen, S. Ebadi, P. Wahid, and X. Gong, "Tunable and flexible Barium Strontium Titanate (BST)

- varactors on Liquid Crystal Polymer (LCP) substrates," 2012 IEEE International Microwave Symposium, Montreal, Quebec, Canada, June 2012.

- [10] T. Matsumura, M. Esashi, H. Harada, and S. Tanaka, "Multi-band radio-frequency filters fabricated by using polyimide-based membrane transfer bonding technology," J. Micromech. Microeng., vol.20, 095027, 2010.

- [11] S.-K. Choi, D.-P. Kim, C.-I. Kim, and E.-G. Chang, "Damage in etching of Ba, SrTiO<sub>3</sub> thin films using inductively coupled plasma," J. Vac. Sci. Technol. A, vol.19, no.4, pp.1063–1067, 2001.

- [12] P.-S. Kang, K.-T. Kim, D.-P. Kim, and C.-I. Kim, "Study of reduction of (Ba<sub>0.6</sub>,Sr<sub>0.4</sub>)TiO<sub>3</sub> thin films etched in Ar/CF<sub>4</sub>," J. Vac. Sci. Technol. A, vol.21, no.4, pp.1469–1474, 2003.

- [13] R.T. Zhang, C.R. Yang, A. Yu, B. Wang, H.J. Tang, H.W. Chen, and J.H. Zhang, "Wet chemical etching method for BST thin films annealed at high temperature," Appl. Surf. Sci., vol.254, no.21, pp.6697–6700, 2008.

- [14] S.-T. Chang, J.Y.-M. Lee, "Electrical conduction mechanism in high-dielectric-constant (Ba<sub>0.5</sub>,Sr<sub>0.5</sub>) TiO<sub>3</sub> thin films," Appl. Phys. Lett., vol.80, no.4, pp.655-657, 2002.

(平成 24 年 9 月 4 日受付, 12 月 21 日再受付)

### 森脇 政仁

2010 東北大・工・機械知能・航空工学 卒. 2012 同大大学院工学研究科ナノメカニクス専攻博士課程前期 2 年の課程了. 修士論文研究として本研究に従事. 2012 から大日本印刷(株)研究開発センター次世代 MEMS 研究所に勤務.

### 掘露伊保龍

Ivoyl P. Koutsaroff is a Chief Research Engineer at Technology & Business Development Unit, Murata Manufacturing Co., Ltd. in Kyoto, Japan. He received his M.Sc. degree in applied physics from Sofia University in 1986,

and his Ph.D. degree in Condensed Matter Physics from Sun Yat-Sen University and Institute of Semiconductors in 1993. He has held research and development positions at the University of Toronto, Canada, and ETL, AIST in Tsukuba. Prior to joining Murata in 2005, since 1998, he had held several engineering positions in Canadian microelectronic industry, where he has been engaged in manufacturing and development related primarily to the (Ba,Sr)TiO<sub>3</sub> thin film decoupling and tunable capacitors. He has authored more than 60 publications in the ferroelectric thin film field, and holds a dozen patents.

## 門田 道雄 (正員:フェロー)

東北大学大学院電気通信工学研究科了 後,1974 村田製作所に入社.1994 工博。 同社元フェロー. 現顧問. 弾性表面波を用いた種々のデバイスの開発と実用化に従事. それらの業績に対して大河内記念技術 賞(1994,2003,2011),紫綬褒章(2005),

IEEE Outstanding Paper Award (2010), 市村産業賞本賞 (2011) ほか多数受賞. IEEE フェロー. 2007~2008 IEEE UFFC 日本支部長. 2008 日本音響学会関西支部支部長.

## 江刺 正喜 (正員)

1971 東北大・工・電子工学卒. 1976 同 大大学院博士課程了. 工博. 同年より東北 大学工学部助手, 1981 助教授, 1990 より 教授となり, 同大学院工学研究科付属マイ クロ・ナノマシニング研究教育センター長 等を経て, 現在, 東北大学原子分子材料科

学高等研究機構教授,兼マイクロシステム融合研究開発センター長. 2004~2006 仙台市地域連携フェローほか,公職を歴任. 半導体センサ,マイクロマシニングによる集積化システム, MEMS などの研究に従事. 著書「半導体集積回路設計の基礎」,培風館 (1981) ほか多数. 河北文化賞 (2005),紫綬褒章 (2006) ほか多数受賞.

# 田中 秀治

1996年4月日本学術振興会特別研究員. 1999年3月東京大学大学院工学系研究科 産業機械工学専攻博士課程了. 1999年4 月東北大学大学院工学研究科助手. 2001年 4月同講師. 2003年4月同助教授. 2004 年1月~2006年3月科学技術振興機構研

究開発戦略センターフェロー(兼務)。2006 年 4 月同特任フェロー、博士(工学)。2010 年 9 月~2011 年 3 月ルーベンカトリック大学客員教授として IMEC に滞在、科学技術分野の文部科学大臣表彰若手科学者賞 (2009)、ドイツ・イノベーション・アワード (2012) ほか 7 件受賞、集積化技術、MEMS パッケージング技術、RF MEMS、Power MEMS、過酷環境向けMEMS などの研究に従事。